Home | Projects | Notes > ARM Cortex-M3/M4 Processor > Access Levels & Operation Modes of the Processor

Access Levels & Operation Modes of the Processor

This section applies to ARM Cortex M0/M3/M4 Processors. If you are using any other processors, please consult the corresponding document.

Operational Modes

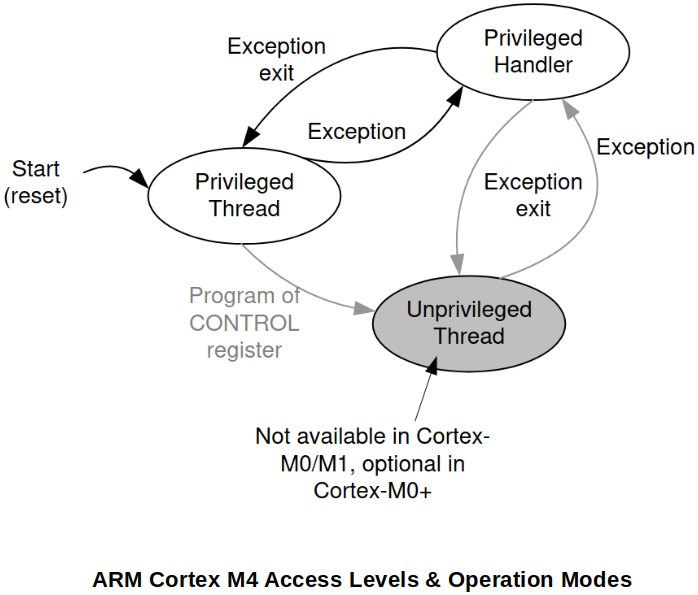

The processor provides 2 operation modes:

Thread mode (User mode)

All program code will execute under "Thread mode" of the processor by default. It can be privileged (full access to CPU resources) or unprivileged (limited access to CPU resources) software execution.

Handler mode

All the exception handlers (or interrupt handlers) will run under the "Handler mode" or the processor. It is ALWAYS privileged software execution.

The processor always starts with "Thread mode".

When there occurs a system exception or any interrupt (HW, SW) then the core will transition to "Handler mode" in order to service the Interrupt Service Routine (ISR) associated with the system exception or the external interrupt. (Only by triggering a system exception or an interrupt, the processor can transition into "Handler mode").

Access Levels

The processor provides 2 access levels:

Privileged Access Level (PAL)

Code running with PAL has a FULL access to all the processor specific resources and the restricted registers. Program will run with PAL by default.

Non-Privileged Access Levels (NPAL)

Code running with NPAL has a LIMITED access to the processor specific resources and the restricted registers.

When the processor is in "Thread mode" with PAL, it is possible to change its access level to NPAL. Once the processor's access level changes from PAL to NPAL, then it is NOT possible for the processor to come back to PAL unless the processor operation mode transitions into "Handler mode" first.

When a program runs in "Handler mode", its access level will always be PAL.

Use the CONTROL register of the processor to switch back and forth between the access levels.

Every program will start running with PAL, and the Control Register must be modified to change the program's access level to NAPL.

Secured & Robust System Design

An RTOS project has two components; the kernel and the user tasks. It is important that user tasks do not modify the system level setting of the processor. So, before running a user task, the kernel should change the access level to unprivileged, and then launch the user task.

This is why, the real-time operating system or secured systems always launch user task in unprivileged access level. If the code running with unprivileged access level wants any services, then it can trigger system call, which will be serviced by the kernel.

This is a secured and robust system design. ARM Cortex Mx processors give these features in the processor itself.

Operation Modes - Demonstration

The program to demonstrate switching between "Thread mode" and "Handler mode".

xxxxxxxxxx5512345678/*9* THREAD MODE : Privileged/Unprivileged access level10* HANDLER MODE : Privileged access level only!11*/1213/*14* This function executes in THREAD MODE of the processor.15* Within this function, we are triggering software interrupt by accessing the16* system level registers of the ARM Cortex Mx processor.17*/18void generate_interrupt()19{20uint32_t *pSTIR = (uint32_t *)0xE000EF00;21uint32_t *pISER0 = (uint32_t *)0xE000E100;2223// enable IRQ3 interrupt24*pISER0 |= (1 << 3);2526// generate an interrupt from software for IRQ327// (interrupt handler "RTC_WKUP_IRQHandler" will be invoked)28*pSTIR = (3 & 0x1FF);29}3031/*32* This function executes in THREAD MODE of the processor.33* (Remember, after reset, the processor always starts in THREAD MODE.)34* In reality, "Reset_Handler:" is the first function to be called on reset,35* but at this point we will assume that the "main" is the first to be called.36*/37int main(void)38{39printf("Thread mode: before interrupt\n");40generate_interrupt();41printf("Thread mode: after interrupt\n");4243/* Loop forever */44for(;;);45}4647/*48* This function (ISR) executes in HANDLER MODE of the processor.49* In HANDLER MODE, you have the full control over the processor. You have the50* privilege to access any resources you want.51*/52void RTC_WKUP_IRQHandler(void)53{54printf("Handler mode: ISR\n");55}How do you know whether the the program is running in "Thread mode" or "Handler mode"?

ISR_NUMBERfield of Interrupt Program Status Register (IPSR).Thread mode if

ISR_NUMBER= 0Handler mode if

ISR_NUMBER= non-zero (only when system exception or interrupt (HW, SW) occurs)Set a break point at L56, and you will see that the

ISR_NUMBERfield is set to 19 (10011(2)) when the execution reaches there.

Consult the Cortex-M4 Devices Generic User Guide for more information.

Access Modes - Demonstration

The program to demonstrate switching between "Privileged mode" and "Non-privileged mode".

xxxxxxxxxx8912345678/*9* THREAD MODE : Privileged/Unprivileged access level10* HANDLER MODE : Privileged access level only!11*/1213/*14* This function executes in THREAD MODE of the processor.15* Within this function, we are triggering software interrupt by accessing the16* system level registers of the ARM Cortex Mx processor.17*/18void generate_interrupt()19{20/*21* These are ARM Cortex M4 processor's system control register addresses which22* can only be accessed in PRIVILEGED ACCESS LEVEL.23* Any attempt to change the contents of these registers from being in UNPRIVILEGED24* ACCESS LEVEL will cause a processor fault exception.25*/26uint32_t *pSTIR = (uint32_t *)0xE000EF00;27uint32_t *pISER0 = (uint32_t *)0xE000E100;2829// enable IRQ3 interrupt30*pISER0 |= (1 << 3);3132// generate an interrupt from software for IRQ333// (interrupt handler "RTC_WKUP_IRQHandler" will be invoked)34*pSTIR = (3 & 0x1FF);35}3637void change_access_level_unpriv(void)38{39/*40* To make the processor transition into UNPRIVILEGED ACCESS LEVEL,41* bit 0 of the CONTROL register must be set to 1.42* CONTROL register is NOT a memory mapped register which means that43* it is impossible for a programmer to access this register using C44* code only. Inline assembly technique is necessary.45*/46__asm volatile("mrs r0, CONTROL"); // read47__asm volatile("orr r0, r0, 0x01"); // modify48__asm volatile("msr CONTROL, r0"); // write (this is where access level changes to49// UNPRIVILEGED50}5152/*53* This function executes in THREAD MODE + PRIVILEGED ACCESS LEVEL of the processor.54* (Remember, after reset, the processor always starts in THREAD MODE.)55* In reality, "Reset_Handler:" is the first function to be called on reset,56* but at this point we will assume that the "main" is the first to be called.57*/58int main(void)59{60printf("Thread mode: before interrupt\n");6162change_access_level_unpriv(); // PRIVILEGED -> UNPRIVILEGED63generate_interrupt();6465printf("Thread mode: after interrupt\n");6667/* Loop forever */68for(;;);69}7071/*72* This function (ISR) executes in HANDLER MODE of the processor.73* In HANDLER MODE, you have the full control over the processor. You have the74* privilege to access any resources you want.75*/76void RTC_WKUP_IRQHandler(void)77{78printf("Handler mode: ISR\n");79}8081/*82* This function will be called when a system level register is accessed in a83* program with UNPRIVILEGED ACCESS LEVEL. (Processor fault exception)84*/85void HardFault_Handler(void)86{87printf("Hard fault detected\n");88while(1);89}Summary:

The program first runs in THREAD MODE with PRIVILEGED ACCESS LEVEL.

We set the bit 0 of the CONTROL register to 1 to change the access level to UNPRIVILEGED.

The program tries to access the system control register which is not allowed with UNPRIVILEGED ACCESS LEVEL.

Hard fault occurs and the corresponding handler gets called.

Now, how do you go back to PRIVILEGED ACCESS LEVEL? When in UNPRIVILEGED ACCESS LEVEL, you are not allowed to access and modify the CONTROL register, which means you cannot go back to PRIVILEGED ACCESS LEVEL. To make it possible, the processor must first transition into the HANDLER MODE which always runs with PRIVILEGED ACCESS LEVEL. There are two, and only two ways to push the processor to HANDLER MODE:

External interrupt

Exception

When an ISR is invoked, then there the CONTROL register can be modified (bit 0 back to 0). Upon returning back to the THREAD MODE, the access level will have been set back to PRIVILEGED.

References

Nayak, K. (2022). Embedded Systems Programming on ARM Cortex-M3/M4 Processor [Video file]. Retrieved from https://www.udemy.com/course/embedded-system-programming-on-arm-cortex-m3m4/