Home | Projects | Notes > MCU Peripheral Drivers > MCU Bus Interfaces

MCU Bus Interfaces

MCU Bus Interfaces

The Cortex-M4 processor contains 3 external Advanced High-performance Bus (AHB)-Lite bus interfaces: I-Code, D-Code, S bus interfaces.

If the instruction is present in between the memory locations 0x00000000 - 0x1FFFFFFF then the processor will fetch the instruction using I-Code interface.

If the instruction is present outside 0x00000000 - 0x1FFFFFFF range then the processor will fetch the instruction over the system bus.

If the data is present in between the memory locations 0x00000000 - 0x1FFFFFFF then the processor will fetch the data using D-Code interface.

If the data is present outside 0x00000000 - 0x1FFFFFFF range then the processor will fetch the data over the system bus.

The base address of the Flash memory for STM32F407xx microcontroller is 0x08000000. Therefore, we know that the constant data will be fetched over the D-Code bus interface.

Many MCU peripherals are located outside the range 0x00000000 - 0x1FFFFFFF and therefore uses system bus interface to communicate.

[!] Note: Since these bus interfaces belongs to the processor, you need to reference the documentation of the processor (not microcontroller) to learn more about them.

Data and Storage

xxxxxxxxxx221234/* String literal (constant data) - Will be stored in ROM (Flash memory) */5const char *pMessage = "Hello world!";67/* Constant data - Will be stored in ROM (Flash memory) */8const int value = 100;910/* Variable data - Will be stored in SRAM */11char data[50];1213int main(int argc, char *argv[])14{15for (uint32_t i = 0; i < strlen(pMessage); i++)16{17/* Data copy from Flash to SRAM */18data[i] = *(pMessage + i);19}2021for (;;);22}

Bus Matrix

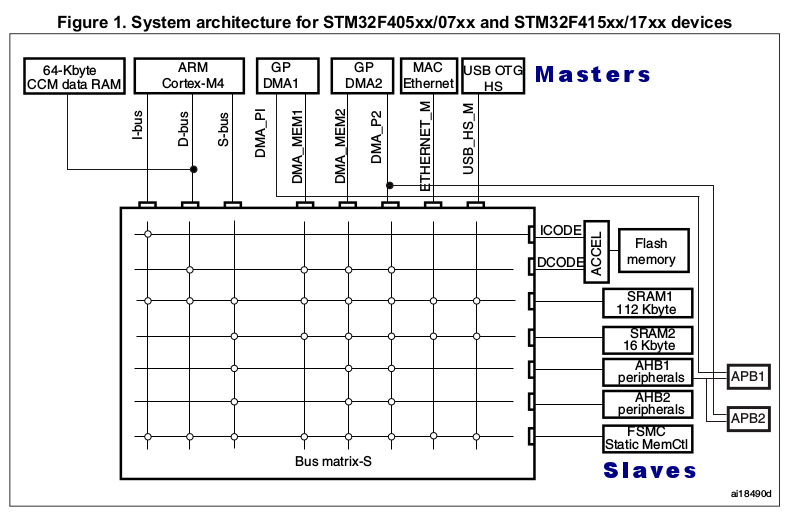

The AMBA bus specification is a multi-master bus standard. As a result, a bus arbiter is required to ensure that only one bus master has access to the bus at any particular time.

The following diagram shows which master can communicate with which slaves via which bus.

Analyzing MCU Block Diagram

Reference: STM32F407xx MCU

Is the system bus connected to Flash memory?

Can processor fetch instructions from SRAM over I-Code?

What's the maximum speed at which the system bus can operate?

Are SRAMs connected to the system bus?

What's the maximum speed at which the APB1 can operate?

Suppose I have a peripheral whose operating frequency or speed must be greater than 95 MHz, can I connect it via APB2 bus?

Can processor fetch instructions and data simultaneously from SRAM?

Can processor fetch instructions and data simultaneously from Flash?

What's the maximum HCLK frequency?

What's the maximum P1CLK frequency?

What's the maximum P2CLK frequency?

Do GPIOs and processor communicate over AHB1 bus?

Do USB OTG and processor communicate over AHB2 bus?

Can OTG and GPIOs communicate with processor concurrently or simultaneously?

Can processor talk to Flash memory and SRAM simultaneously?